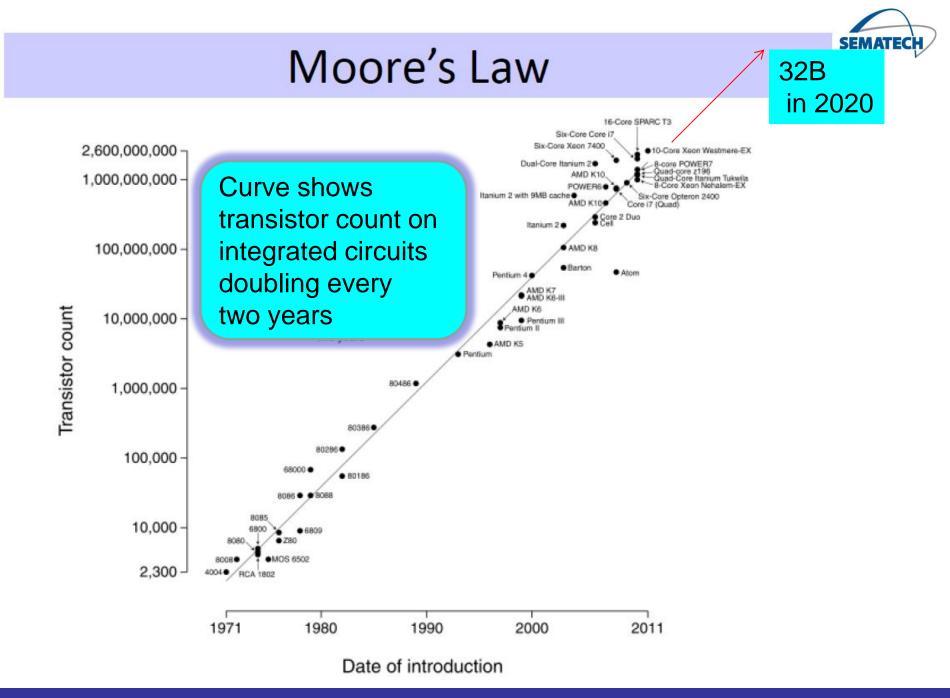

#### Accelerating the next technology revolution

# More Moore or More than Moore?

Copyright ©2009

SEMATECH, Inc. SEMATECH, and the SEMATECH logo are registered servicemarks of SEMATECH, Inc. International SEMATECH Manufacturing Initiative, ISMI, Advanced Materials Research Center and AMRC are servicemarks of SEMATECH, Inc. All other servicemarks and trademarks are the property of their respective owners.

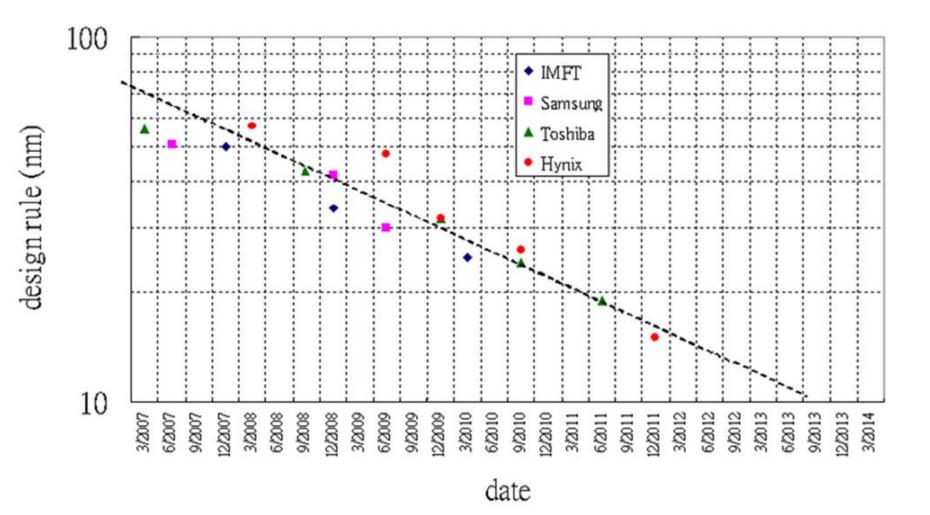

NAND flash memory trend allows doubling of components manufactured in the same wafer area in less than 18 months.

### **Technology Trends**

1990s

(2011 GSA Forum, Nvidia, 2011 KSIA, Dongbu)

# **Industry Trends**

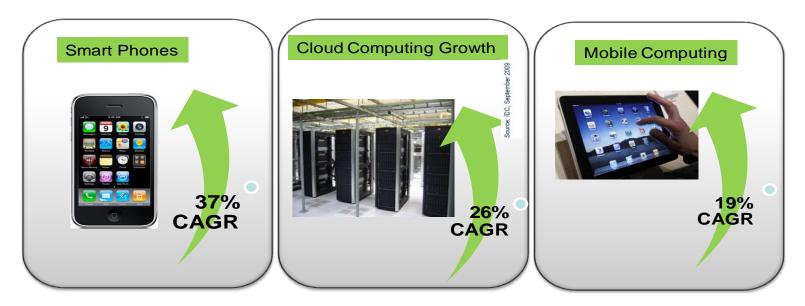

### • System Drivers:

- Low and ultra-low power logic with multi-core/multi-modules

- Dense 3D NVM RAM for Solid-State Disc (SSD) and dense DRAMs (TB)

- High-level of functional integration (Digital, analog, RF, NVM, DRAM, MEMS, low power displays,...)

- Faster data transfer needs between modules and between chips

- Significant gaps leads to device transitions

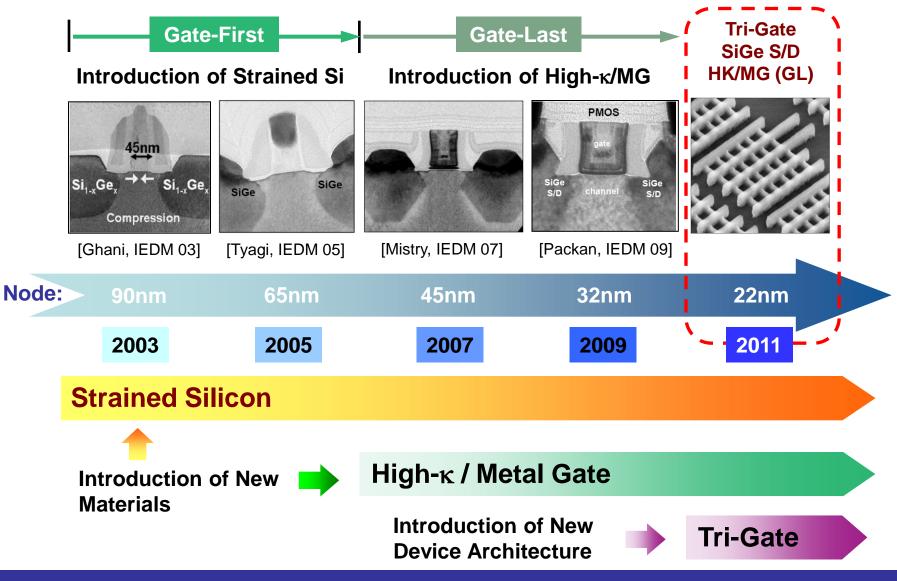

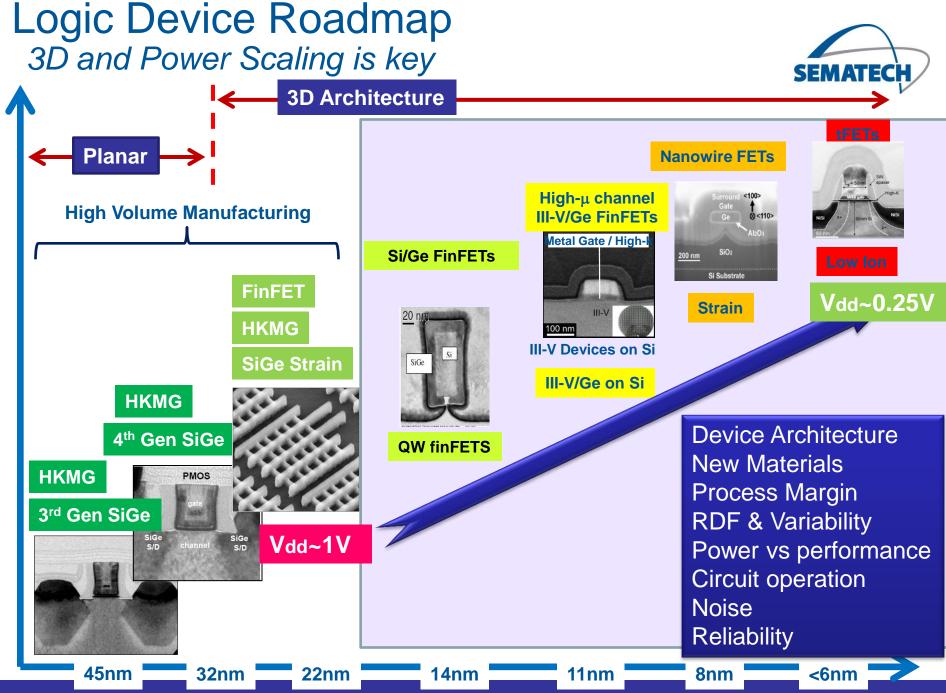

### New materials & device architectures

Can we continue performance roadmap with litho scaling alone?

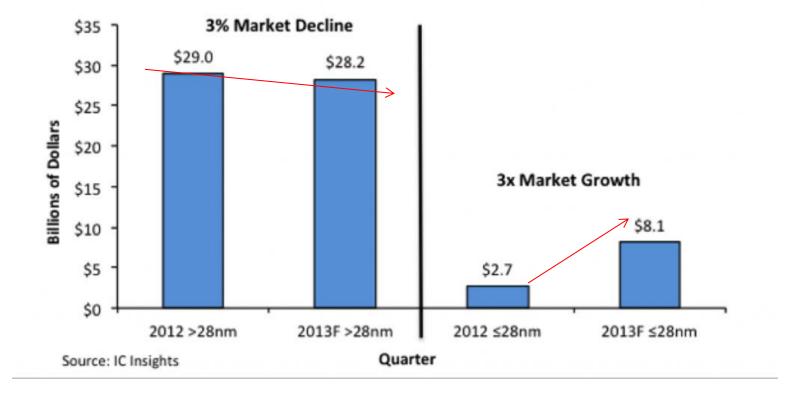

### 2013: Sub-28nm increasing in market growth

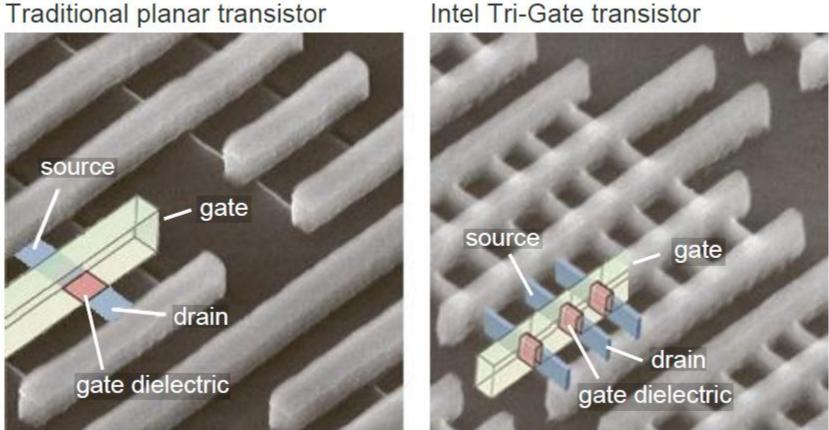

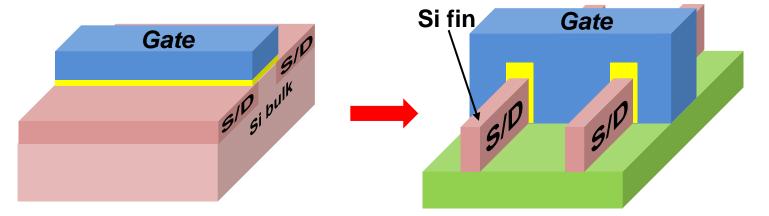

#### Traditional planar transistor

Gate dielectric shown in red

- Traditional  $\rightarrow$  planar •

- Tri-gate  $\rightarrow$  3D •

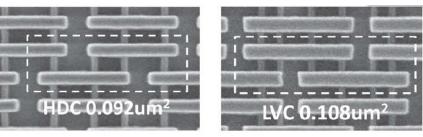

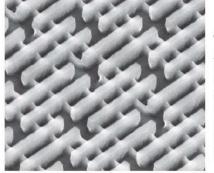

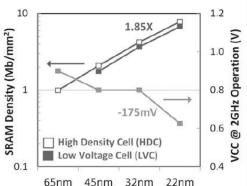

## **22nm Tri-Gate Announcements**

\*Mark Bohr, Kaizad Mistry: Intel, April 25th, press release

http://semimd.com/blog/2012/04/10/finfetshkmg-on-2012-vlsi-symposium-program/

#### \*ISSCC 2012, p229-230

22nm Tri-Gate LVC SRAM Array

# Issued by: TSMC – Sept. 17, 2013 – "TSMC released Innovation 16FinFET systems-on-chip (SoC) designs....."

http://www.tsmc.com/tsmcdotcom/PRListingNewsAction.do?action=detail&ne wsid=8041&language=E

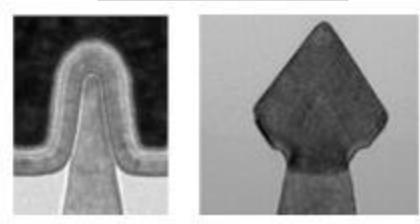

## Improving Electrostatics: FinFETs

**Conventional Planar FET**

FinFET (Multi-Gate FET)

- 1) Strong immunity to short-channel effects

- supports smaller  $L_{eff}$  at same  $I_{off}$

- 2) Better performance

- supports smaller  $V_{TH}$  at same  $I_{off}$

- 3) Low doping

- supports higher  $\mu$  & improved random dopant fluctuation

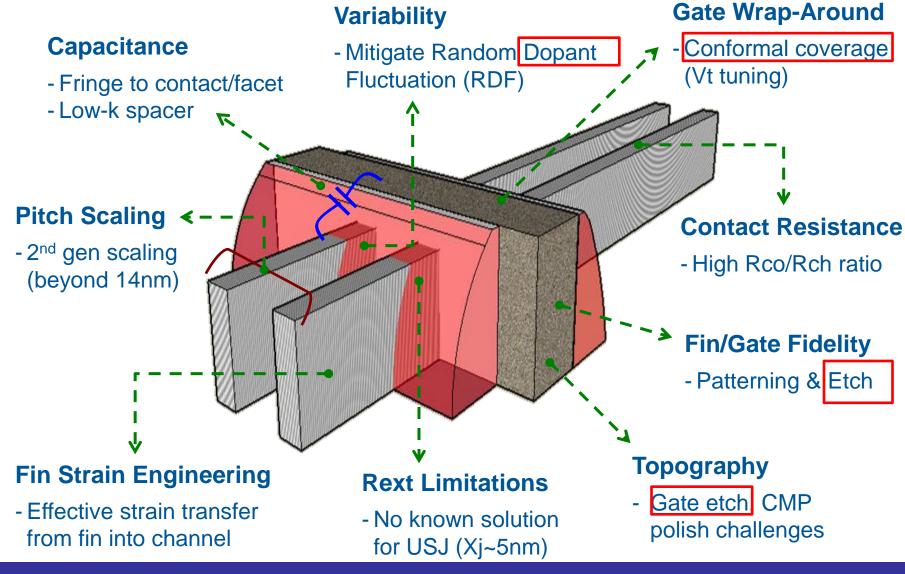

# FinFET/tri-gate scaling challenges

# Non-Si (High-µ) Channel Materials

|                                               | Si                                               | Ge                                                | GaAs                                              | InAs                                             | InP                                              | InSb                                              |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------|---------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------------------------------------------------|

| Electron mobility<br>(cm²/Vs)                 | 1600                                             | 3900                                              | 9200                                              | 40000                                            | 5400                                             | 77000                                             |

| Electron effective<br>mass (/m <sub>o</sub> ) | m <sub>t</sub> : 0.19<br>m <sub>l</sub> : 0.916  | m <sub>t</sub> : 0.082<br>m <sub>l</sub> : 1.467  | 0.067                                             | 0.023                                            | 0.082                                            | 0.014                                             |

| Hole mobility<br>(cm²/Vs)                     | 430                                              | 1900                                              | 400                                               | 500                                              | 200                                              | 850                                               |

| Electron effective<br>mass (/m <sub>o</sub> ) | m <sub>HH</sub> : 0.49<br>m <sub>LH</sub> : 0.16 | m <sub>HH</sub> : 0.28<br>m <sub>LH</sub> : 0.044 | m <sub>HH</sub> : 0.45<br>m <sub>LH</sub> : 0.082 | m <sub>HH</sub> : 0.57<br>m <sub>LH</sub> : 0.35 | m <sub>HH</sub> : 0.45<br>m <sub>LH</sub> : 0.12 | m <sub>HH</sub> : 0.44<br>m <sub>LH</sub> : 0.016 |

| Band gap (eV)                                 | 1.12                                             | 0.66                                              | 1.42                                              | 0.36                                             | 1.34                                             | 0.17                                              |

| Permittivity                                  | 11.8                                             | 16                                                | 12                                                | 14.8                                             | 12.6                                             | 17                                                |

- InGaAs : High electron mobility (light effective mass) → nMOSFET

- Ge : High hole mobility (light effective mass) → pMOSFET

- Band gap, permittivity & density of state ; negative effects

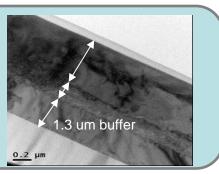

STI

Si subsucte

15 nm 5 nm

nMOS buffer

30 nm

5 nm

pMOS butter

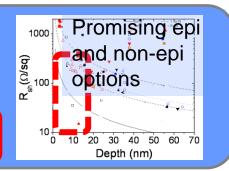

### Au-free Contacts:

Thermal stability?, alignment? cleans...

#### Scaled Gate Stacks:

Surface passivation?, Interface layer?, HKMG Clustered tools?

### Defect-free Junctions:

Epi, I/I, Plasma, Monolayer Doping [MLD]

1000A In(53%)GaAs, N<sub>.</sub>(Si) =5e19/cm

10

CET (nm)

#### **III-V on Si** Thin buffer?, XOI? Large wafers ?

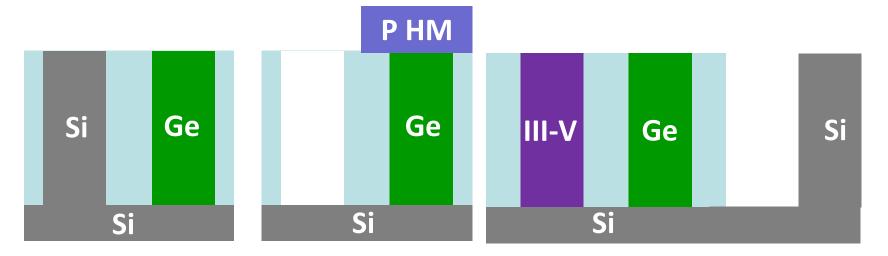

### Heterointegration of Ge & III-V on Si for SOC Three semiconductors on same chip!

#### Ge on 300mm Si

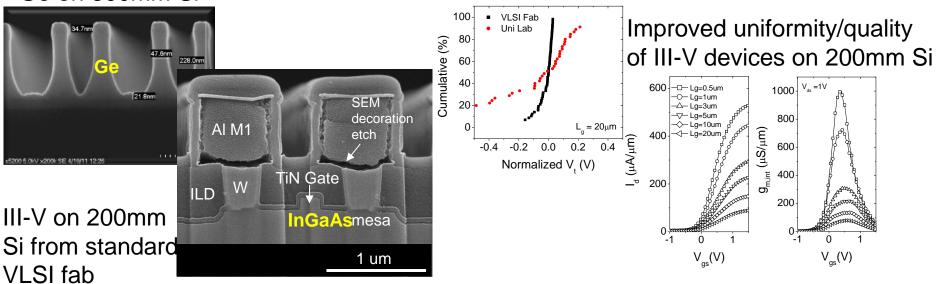

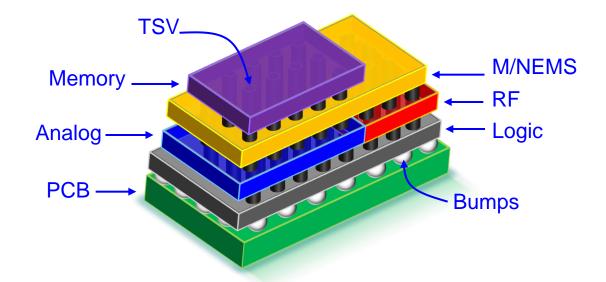

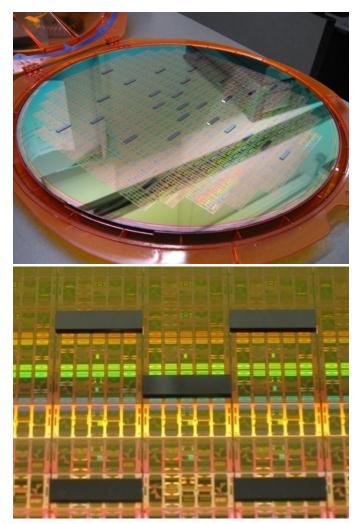

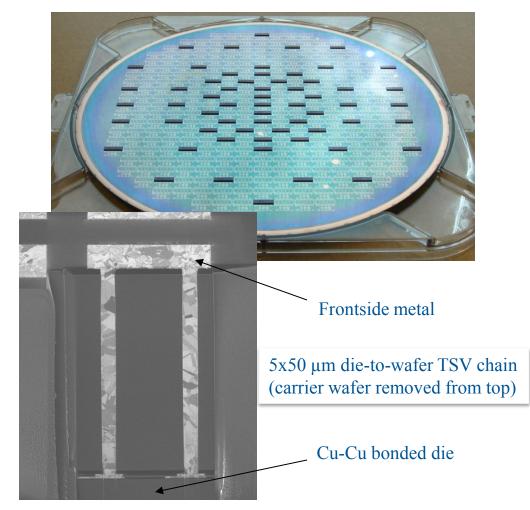

# 3D means different things to different people ...

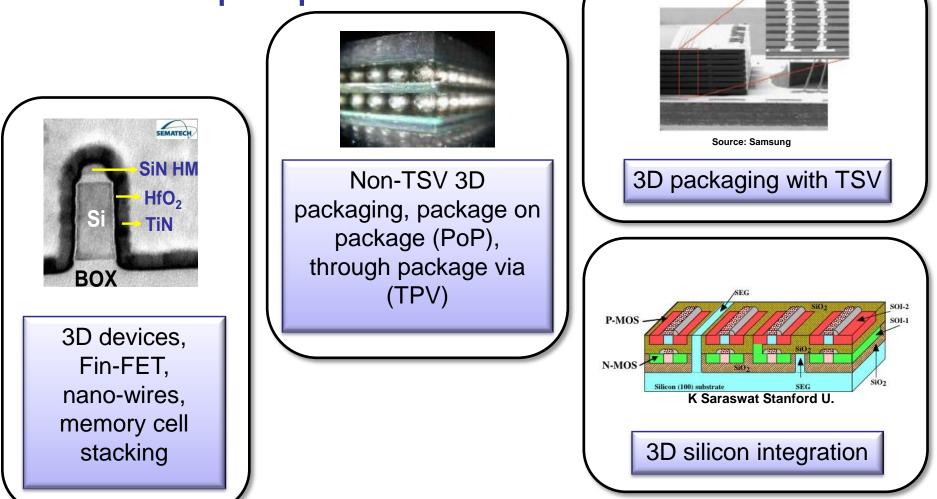

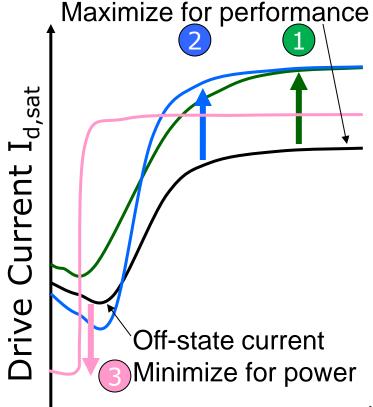

# **Power Management**

The end of "traditional" scaling is near: But  $\rightarrow$  Performance enhancement greatly increases power consumption.

- Passive power has shown continuous increase due to V<sub>DD</sub> scaling limit.

- $V_{CC}$  scaling limited by  $V_T$  and subthreshold slope (which is kT/q limited)

### $\rightarrow$ need "green" devices not governed by kT/q ~ 60mV/dec limit.

### Power Performance Trade-offs Beyond CMOS Opportunities → CMOS+

On state current

### Gate Voltage

- High Mobility materials

- SiGe, Ge, InGaAs

- Graphene [ $\mu_e \sim 15000 \text{ cm}^2/\text{V-s}$  at RT]

- Better electrostatic control

- Multiple gates + more channel area

- FinFETs, nanowire FET

- Improve on-off ratio

- Tunnel FET

- Very steep ΔSS << 60 mV/dec</li>

- Low bias voltages (<< 1V)</li>

- Nano Electro Mechanical switch (NEMS)

- Hybrid: I<sub>on</sub> by CMOS + I<sub>off</sub> by NEMS

- Zero off-state leakage, Low Power

#### Logic and Memory Technology Scaling Materials and novel structures driven SEMATECH Beyond CMOS Materials/Structures **Advanced Materials Advanced Structures Logic** High $\mu$ Metal Gate / High-I Fin/N₩ SEMATECH High u Si **Bulk/SOI Si** III-V **Bulk/SOI Si** 100 nm Sí SiG Gate stack Channels, contacts, USJ NEMS **III-V Devices on Si** High mobility Fins/Nanowires SEMATECH Metal Graphene High-k High-ĸ Si InGaAs SiGe SiGe 2nm SEMATECH EMATECH TFET 2010 2020 **Memory** EMATECH TIN wox "0.0"state RRAM w **STTRAM** 50nm Cross-point TIN HIOX **ReRAM/Nanowire** <20nm **RRAM CT Flash 3DArray** RRAM

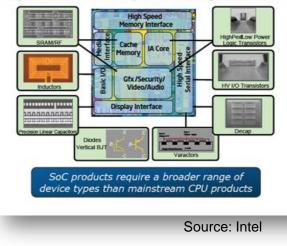

Compute – MPU, GPU Store – NAND, DRAM, NOR, SRAM Communicate – WiFi, 3G/4G, BlueTooth Sense – Orientation, GPS, Touch, ... Interface – HD, Touch, Voice commands, Camera

### High Level of Functional Integration Where-ever, When-ever, What-ever

## **Technology Trends: New Drivers**

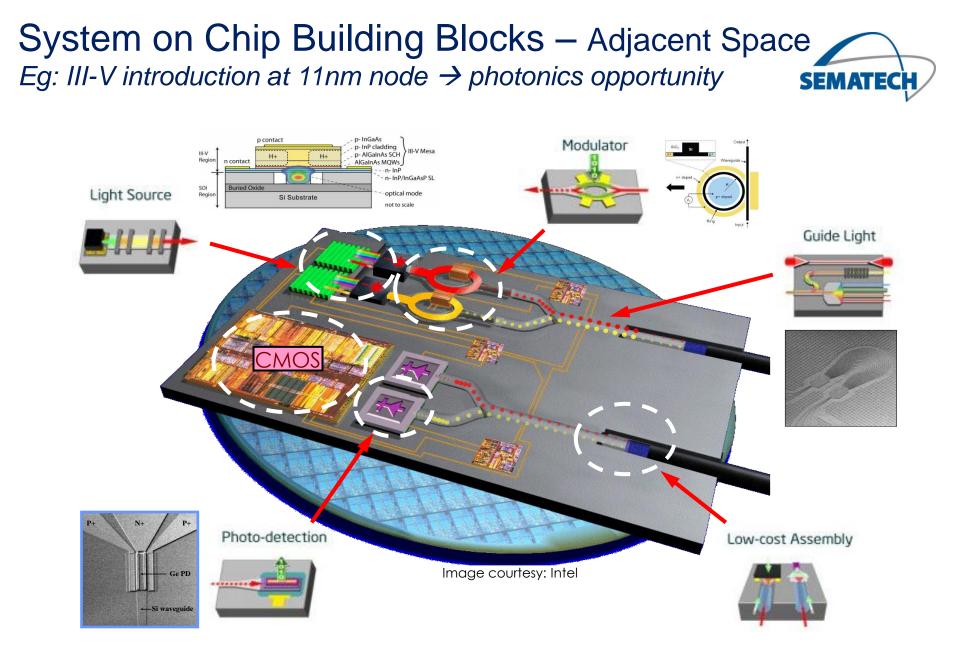

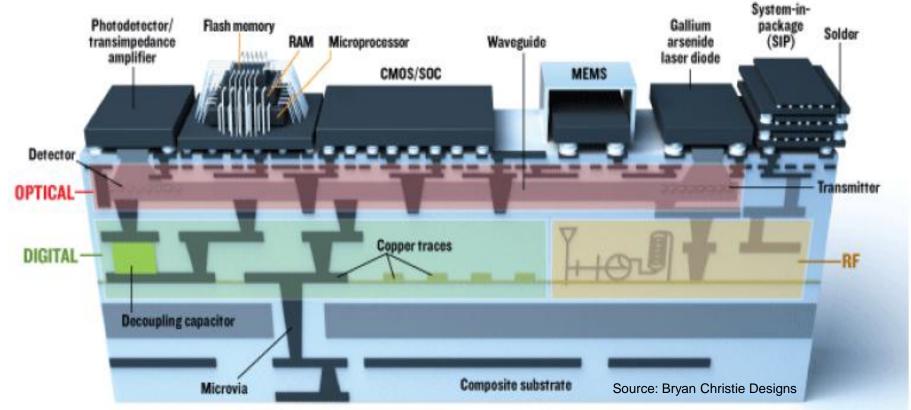

#### System-on-Chip Building Blocks

### System-on-a-Chip (SOC)

- Enables low power, low form factor solutions

- Minimal performance compromise

- Integrate MPU/GPU with analog, RF, NV memory

- High performance

### System-in-a-Package (SIP)

- Enables low power, low form factor solutions

- Minimal performance compromise

- Integrate MPU/GPU with analog, RF, NV memory

- High bandwidth

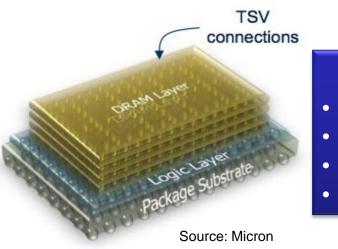

### Key Enabler: 3 Dimensional Integration (3DI)

- Transitioning into 3D technology will enable the continued proliferation of electronics into diverse domains.

- Further development is needed to meet the challenges of this transition;

# **3D Stacking**

#### Enables system-level scaling of performance

# Vision of Future

Use best suited material/device based on functional need

Self-powered system in your pocket!

# Summary

- CMOS or Beyond CMOS is <u>NOT</u> the question

- Sense, compute, store, transmit: Integrated functionality

- Convergence of technologies is the future

- System level power reduction with performance gain is key

- Functional diversity vs device density

- •Focus of miniaturization shifts to adding diverse components

- •CMOS+ : Hybrid integration of beyond-CMOS with CMOS

- •Challenge: How can we fabricate them and make them work seamlessly

- •All systems are driven by mobile needs

- Logic and memory are 3D for density, performance/watt

- 3D Interconnects is a game changer

- Rich opportunity space for industry growth

Need for strong collaborative models to reduce risk and cost